## 低環境負荷酸化物エレクトロニクスのための高誘電率超格子

# バッファ層の創製

## Creation of super-latttice buffer layer with high dielectrics constant for

### environmentally-friendly oxide electronics

#### 代表研究者

東京工業大学総合分析支援センター助手 木口賢紀 Center for Advanced Materials Analysis, Tokyo Institute of Technology; Research Associate, Takanori Kiguchi

現在,我々の生活のあらゆる分野にエレクトロニクスが不可欠となり,デバイスのさらなる小型化, 高集積化,省エネルギー化が必須の課題となっている.これらの要求は,他方で環境負荷の削減につな がるため,便利さの向上・環境改善と一石二鳥の効果をもたらす.そのために,Siデバイスに種々の酸 化物を融合することによって,従来のSiデバイスではなしえない高機能性が達成されつつある.Siデバ イスは,電界効果トランジスター(FET)をベースにしており,FET に流れる電流制御のためのゲート絶縁 膜/Si積層界面が最重要部位である.デバイスの性能はこの界面の電気特性の如何にかかっている.本 研究は,Zr0,Ti0,を原子レベルで超格子化した新しいゲート絶縁膜の創製を目指し,ゲート部への電界 印加効率の大幅な向上により,省エネルギー化・環境負荷削減のための低電圧駆動型Siデバイスの基礎 として社会への貢献が期待される.

It becomes important that the down sizing of electronics devices, which requires lower operating voltage. This study aims the creation of next-generation gate dielectrics with higher dielectric constant than existing one in order to satisfy the demand. Zirconia (ZtO<sub>2</sub>) is a promising material that has high dielectric constant (~25), wide energy band gap (~5.6eV), large band offset with Si conduction band (~1.4eV), thermal and chemical stability, and so on. Furthermore, our previous studies shows that zirconia has excellent compatibility with Si wafer; 1. Zirconia can be easily epitaxially grown on Si(001) wafer through amorphous-like Si oxide layer within 2nm. 2. Pure zirconia without any stabilizing dopant, which shows monoclinic phase in the thicker zirconia film, shows tetragonal phase in the thickness less than 3nm. Thus, zirconia is suitable for the gate dielectrics. The oxide electronics devices such as ferroelectric memory, however, will be operated at lower voltage if the gate dielectrics with higher dielectric constant above 25 is obtained. On the other hands, titania (TiO<sub>2</sub>), has higher dielectric constant as much as 80. The leakage current of titania, however, is too high to be used as gate dielectrics because of little band offset with Si. Then, I have given grate attention to the combination of zirconia and titania in a super-lattice structure. The point of the idea is to take advantage of the high dielectric constant of titania and the high electric insulation (low leakage current) of zirconia. This study will put the oxide electronics devices with lower operative voltage into practice. Therefore, it will contribute to reduce not only the downsizing of devices, but also the effects on the environment.

#### 1. 研究目的

酸化物エレクトロニクスにおいて,強誘電体薄 膜等の電子・光学セラミック薄膜とシリコン基板 との間の,電気的・結晶学的な欠陥を可能な限り 抑制しながら両者を接合するためにバッファ層 (緩衝層)と呼ばれるゲート絶縁膜が積層されて いる. Si(001)基板上へのエピタキシャル成長,高 い比誘電率(以下誘電率と表記),高い絶縁性,

薄膜基板間の元素の相互拡散ブロック、熱的・化 学的安定性などの観点から、申請者はエピタキシ ャル Zr0, (ジルコニア) バッファ層の有効性を見 出してきた. しかし, 高温成膜過程における Si 基板表面の酸化によって、1nm 程度のSi酸化膜の 再成長が避けられない. これは、ZrO。のもつ高誘 電率(~25)を見かけ上 Si 酸化膜(~3.8)が相殺し てしまい, Zr0,の特徴を生かせなくなっている. よって、Zr0,の誘電率を何らかの方法で向上させ ることで、Si 酸化膜による見かけの誘電率低下を 補償することが必要である. この問題は、これか らの Si あらゆるデバイスの高集積化, 省エネルギ 一化にとって解決が急務である. そこで、本研究 ではリーク電流が高く単独では使用できないが 非常に高い誘電率(~80)を持っている TiO, (チタ ニア)に着目し、高い誘電率と共に高い絶縁性を 持つZrO2とエピタキシャル人工超格子を形成する ことによって、Zr0, 単層ではなしえない高誘電率 を発現させ、かつ Zr0,の高い絶縁性によって Ti0, の低リーク特性をカバーすることが可能となる. また、Zr0。と Ti0。を単に積層するのではなく、単 位格子あるいは原子層レベルで超格子化するこ とによって、2つの材料相互の欠点を補い、互い の長所を引き出すこと、さらに超格子化によって 初めて発現する歪み超格子効果の相乗効果をね らったものである.本研究の様にバッファ層、ゲ ート絶縁膜の分野へのエピタキシャル超格子構 造の応用、並びに Zr0,と Ti0,との組み合わせは世 界的に見ても行われておらず、本研究には独創的 な成果が期待される. そして, 高誘電率エピタ キシャル超格子バッファ層の創製によって、Si デ バイスの低電圧駆動、高集積化による省エネルギ ー酸化物の創製,そして低環境負荷 Si デバイス創 製への突破口を拓くことを目指す.

#### 2. 研究経過

#### 2.1 人工超格子の合成

本研究では、1. Siウエハー上へのCeO<sub>2</sub>/YSZ人工 格子の作製,及び2. Siウエハー上へのTiO<sub>2</sub>/CeO<sub>2</sub>/ YSZ人工格子の作製,3. YSZ/Si及びCeO<sub>2</sub>/Siヘテロ

界面構造制御とSi酸化膜の影響,4.界面電気特性 評価に関して調べた. 初めにCeO,とYSZからなる二 重人工超格子の作製を行った. 成膜にはPLD (Pulsed Laser Deposition)法を使用し、基板温度800℃、酸 素分圧5.5x10<sup>4</sup>Torrの条件下で一定時間ごとに CeO,, 8mo1%Y,0,安定化ZrO,(YSZ)セラミックスターゲ ットを交互に切り替えて各2nmのCeO, YSZからなる 5周期のエピタキシャル人工超格子の堆積を行っ た. 基板はp型(001)Siウエハーを使用した. ただし, IF洗浄は行っていない. これは申請者らが見出し たことであるが、自然酸化膜の存在がYSZ薄膜のエ ピタキシャル成長を促進するためである.一方, TiO<sub>2</sub>/CeO<sub>2</sub>/YSZ人工格子構造についても同様に各層 5周期のエピタキシャル人工格子構造の作製を試 みた. 合成した人工超格子は、X線広域逆格子空間 マッピング法,高分解能電子顕微鏡(HRTEM)法によ りマクローナノスケールの構造評価を行い、容量-電圧(C-V)及び電流密度-電圧(J-V)測定により界面 電気特性の評価を行った.

#### 2. 2 XRD法によるマクロ構造評価

図1にCe0/YSZ人工格子のX線広域逆格子空間マ ップを示す.(b),(c)は全体像(a)のうちCe0/YSZ002, 及び200ピーク近傍を拡大したマップである.(a) からSiウエハーに対してYSZ,Ce0心ずれも層も001 配向のエピタキシャル成長していることが分かる. (b)(c)より歪み膜厚方向,面内方向いずれもバルク のCe0,YSZのピーク位置が大きく変位しほぼ完全 に重なって1本のピークに見える.すなわちエピ タキシャル成長したCe0,YSZ各層が相互の格子ミ スマッチ%を緩和することなく単位格子が大きく 変化して両層が人工超格子を形成していることを 示唆している.なお,僅かではあるが111配向のピ ークも現れている.

一方,図2(a)からSiウエハーに対してYSZ,CeQ いずれも層も001配向のエピタキシャル成長して いるが,TiO2のピークは一切観察されなかった.よ って,TiO2層は非晶質あるいは多結晶であると推定 される.TiO2/CeO2/YSZ人工格子は、(b)膜厚方向では CeO2とYSZのピークが分離しておりほぼバルクのピ

ーク位置に近い.つまり膜厚方向の歪みはほぼ緩和 されていることを示している.一方,(c)面内方向 においても完全ではないがピークが高角側に分離 しかけている.よって,面内方向には格子ミスマッ チによる歪みが残留している.この歪み緩和はTiO, 層がエピタキシャル成長していないことに起因す ると考えられるが,この様なTiO,層を介してCeO,/YSZ 層がエピタキシャル成長を続けるのは極めて興味 深い.なお,図2(b)のCeO,に重なっている赤い鋭い 2本のピークはSiの002禁制反射である.

#### 2. 3 HRTEM法によるナノ構造評価

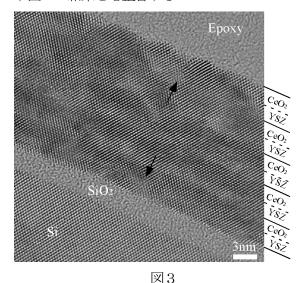

図3にCeO/YSZ人工格子の断面TEM格子像を示す. 界面に多少のラフネスは認められるが、CeO\_/YSZ1 層あたり約3.6nmの人工超格子が形成されている. CeO\_/YSZ界面には格子ミスマッチから予想される ミスマッチ転位密度に比べて転位の数ははるかに 少なく(図中矢印),格子ミスマッチが緩和され ず図1の結果とも整合する.

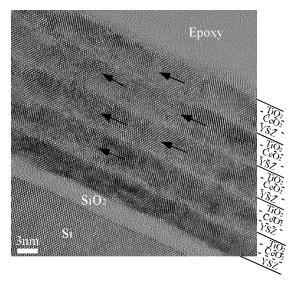

一方,図4に示したTi0,/Ce0,/YSZ人工格子の断面

TEM格子像からTi0,/Ce0,/YSZ1層あたり約4.5nmの人

工超格子が形成されている.なお,各層の組成は

TEM-EDS法により確認した.ラフネスは図3と大

図4

きな違いは認められないが、Ti0,層は配向が大きく 乱れておりエピタキシャル成長せず多結晶薄膜と なっており、XRDの結果図2でTi0,が観察されなかっ たことと符合する.このために、Ce0,/Ti0,/YSZ間で 格子ミスマッチが緩和されたものと考えられる.配 向の乱れたTi0,層の上にYSZ/Ce0,層が再びエピタキ シャル成長している点が興味深いが、YSZ,Ce0,層共 に配向性は低下しモザイク性が高くなっている.

#### 2. 4 界面電気特性

図5に(a)CeO,/YSZ, (b)TiO,/CeO,/YSZのC-V特性を示 す. YSZで問題となる分極型ヒステリシスがほとん どなく超格子化、あるいはYSZ層の超薄膜化の効果 であると考えられる.一方, TiO,/CeO,/YSZではヒス テリシスはほとんど現れていない. また, フラット バンドシフトはCeO,/YSZではほとんどOであったが、 Ti0,/Ce0,/YSZでは+0.5Vであることから、Ti0,層に起 因した負の固定電荷の存在を示唆している. Si0.層 の影響を分離して,蓄積側の酸化膜容量から両超格 子の比誘電率を計算すると、CeO,/YSZで11.2、TiO,/ Ce0,/YSZで19.6の誘電率が得られた. 所望の誘電率 40は得られなかったが、YSZ、CeOかなどで報告されて いる値より高い値が得られた.本実験ではTi0の回 折強度が極めて弱く相同定ができなかったが、ルチ ル相よりもはるかに誘電率の低いアナターゼ相が 生成した可能性が考えられる. また, ルチル相の場 合でもイオン結晶の誘電率は格子振動による格子 分極の寄与が大きいため、 ルチルの高誘電率のa軸 を膜厚方向に配向させる必要がある.

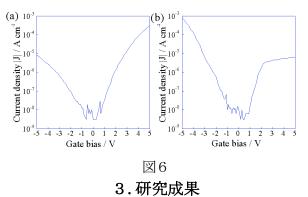

図6に(a)Ce0,/YSZ, (b)Ti0,/Ce0,/YSZのJ-V特性を示 す.両者ともフラットバンド電圧において5-8x 10<sup>9</sup>J cm<sup>2</sup>という良好なリーク特性が得られた.Ti0<sub>2</sub>

というナローバンドギャップの材料が存在しても, ワイドバンドギャップのYSZ/Ce0,層によってリー ク電流をブロックできたことを示している.

本研究により、Ti0<sub>2</sub>/Ce0<sub>2</sub>/YSZ人工超格子が10<sup>o</sup>J cm<sup>2</sup> オーダーの低リーク電流密度を維持しながら、約 20の誘電率が得られた.また、Ti0<sub>2</sub>層は配向性の低 い多結晶層であったが、その上にYSZ/Ce0<sub>2</sub>層が再 びエピタキシャル成長することを見出した.

#### 4. 今後の課題と発展

今後の研究課題としては、TiO。層の結晶相制御, 配向制御,超格子の結晶性向上,界面ラフネスの 抑制が不可欠である.特にTiO。層の結晶相,配向性 の制御が更なる高誘電率化,すなわち低電圧駆動 やモバイル化に不可欠であると言える.そのため には、人工超格子の各層の厚さの最適化,成膜速 度,酸素分圧,基板温度,Si基板表面処理などの 成膜プロセスの更なる最適化が必要である.誘電 率に及ぼす歪み超格子の効果についても更なる検 討が必要である.

#### 5.発表論文 リスト

CeO2/YSZ 積層構造評価について:

木口賢紀,脇谷尚樹,水谷惟恭,篠崎和夫,高 分解能分析電子顕微鏡による CeO<sub>2</sub>/YSZ/Si ヘテ ロ界面構造の原子スケール構造評価,分析化学, 55,6,(2006)印刷中

Ti0,/Ce0,/YSZ 人工超格子のナノ構造評価,界面電気特性については投稿準備中である.